パナソニック:高実装信頼性の半導体パッケージ基板材料を製品化

- 2021/06/22

- Motor Fan illustrated編集部

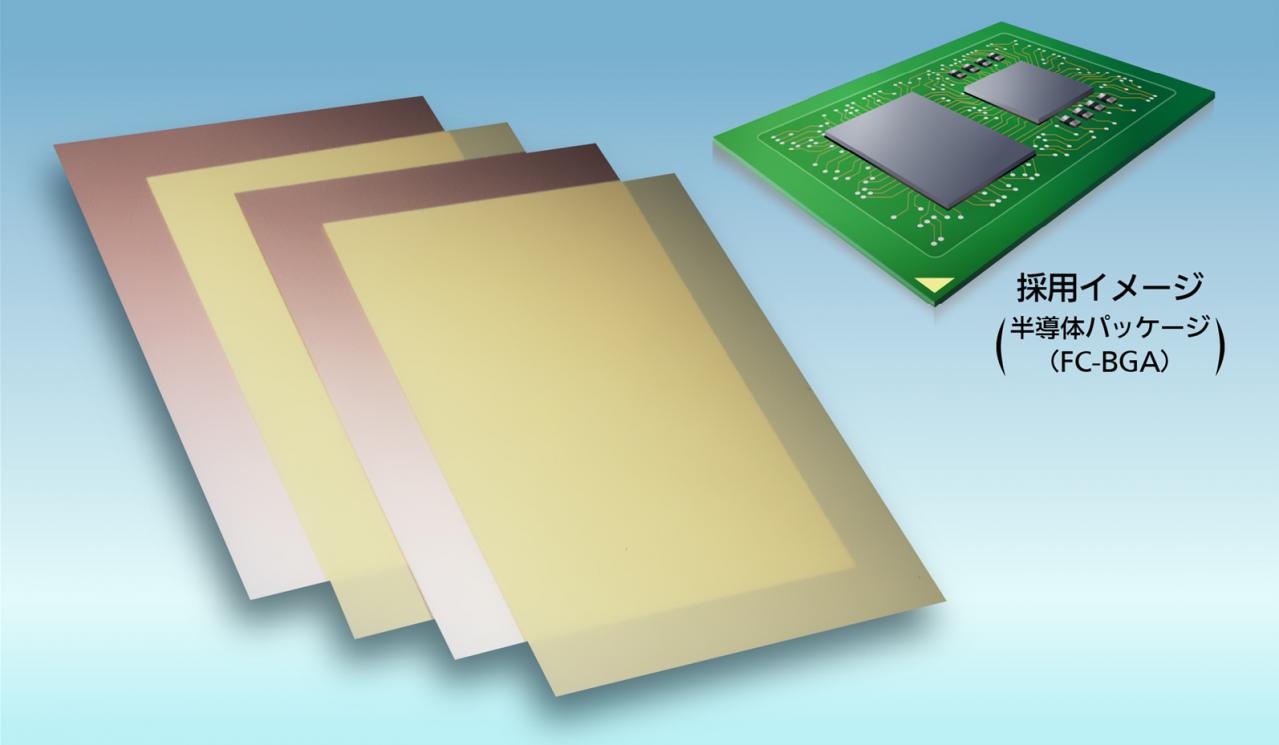

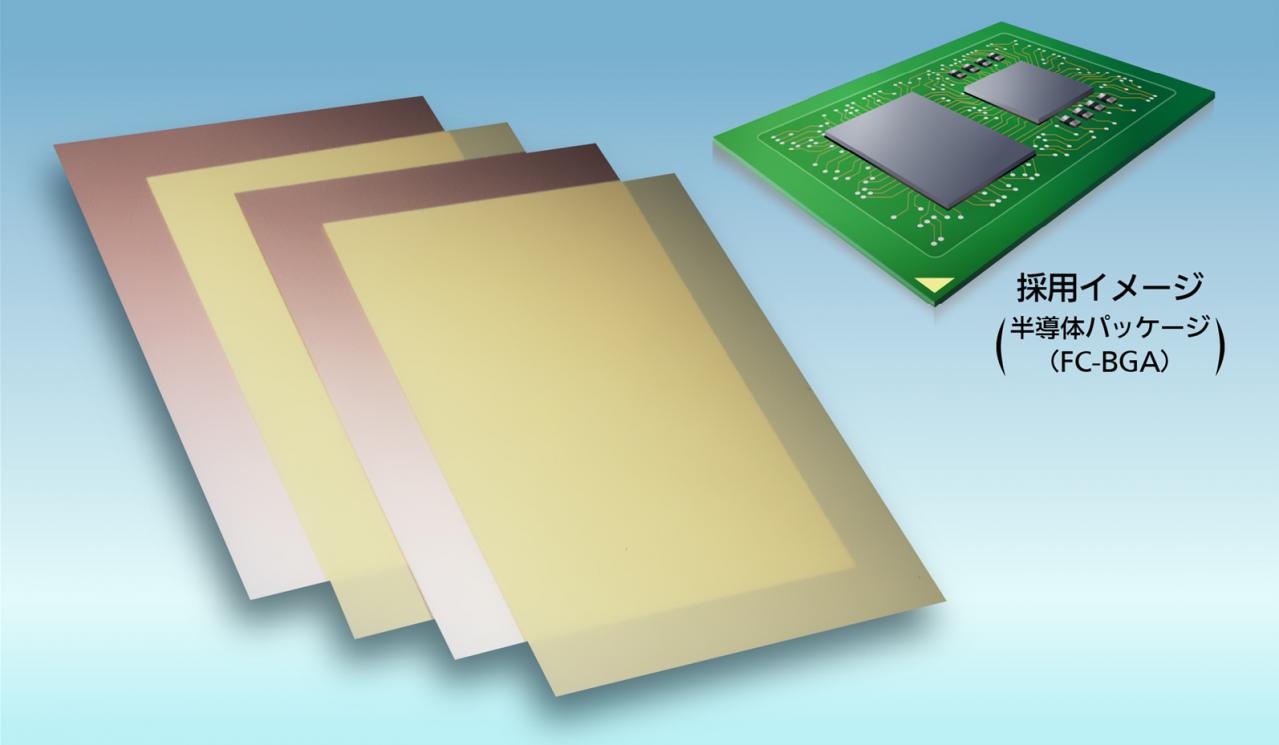

パナソニック インダストリアルソリューションズ社は、実装時に低熱膨張性で反りを抑制するとともに、最適な伸縮性と緩衝性で、はんだボールへの応力低減を実現した高実装信頼性の「半導体パッケージ基板材料:R-1515V」を製品化した。2021年7月より量産を開始する。

IoT、AIテクノロジー、カーエレクトロニクス化を支える半導体は、高性能化・高集積化が進展している。これに伴い半導体パッケージは、大型化や2.5Dパッケージ(※1)に見られる高密度化が進み、高い実装信頼性が求められている。マザーボード用基板材料および半導体材料として半導体パッケージ基板(サブストレート)材料、半導体封止材などの複数の材料を開発しているパナソニックは、これらの独自の開発技術を擦り合わせることで、高い実装信頼性が得られるサブストレート材料を開発した。

実装信頼性を高めるには、ICチップとサブストレートの実装(一次実装)時に反りの発生を抑制することに加え、半導体パッケージとマザーボードの実装(二次実装)時にはんだボールに発生する応力を低減する必要がある。

開発した材料は、熱膨張率(CTE ※2)を抑え、ICチップの低いCTEに近づけることで反りの発生を抑制し一次実装の信頼性を高める。さらに優れた板厚精度によりサブストレートとICチップとの接合を安定させ、一次実装の信頼性の更なる向上に貢献する。二次実装においては、熱膨張差ではんだボールにかかる応力を伸縮性と緩衝性を合わせ持つことにより緩和させ、実装信頼性を向上させる。

<特長>

1. 低熱膨張性でICチップの熱膨張率に近づけ反りを抑制し、ICチップ実装(一次実装)の不具合を低減

2. 低熱膨張性を確保しつつ、樹脂の伸縮性と緩衝性を合わせ持つ応力緩和技術により二次実装の信頼性を向上

3. 板厚精度に優れ、サブストレート(コア材)とICチップとの接合を安定化、一次実装の信頼性を更に向上

<用途>

CPU(※3)、GPU(※4)、FPGA(※5)、ASIC(※6)等のFC-BGA(※7)パッケージ

<備考>

「The 2021 IEEE 71st Electronic Components and Technology Conference」(2021年6月1日~7月4日)において紹介。

※1 2.5Dパッケージ:ロジック半導体とメモリ半導体をインターポーザを介してサブストレートに実装する半導体パッケージの構造タイプ。

※2 CTE:熱膨張率。温度の上昇によって物体の長さ・体積が膨張(熱膨張)する割合を温度あたりで示したもの。

※3 CPU:中央処理装置または中央演算処理装置。

※4 GPU(Graphics Processing Unit):コンピュータゲームに代表されるリアルタイム画像処理に特化した演算装置。

※5 FPGA:製造後に購入者や設計者が構成を設定できる集積回路。

※6 ASIC:電子部品の種別の1つで、特定の用途向けに複数機能の回路を1つにまとめた集積回路。

※7 FC-BGA:LSIチップの高速化、多機能化を可能にする高密度半導体パッケージ基板。

|

|

|

自動車業界の最新情報をお届けします!

Follow @MotorFanwebおすすめのバックナンバー

これが本当の実燃費だ!ステージごとにみっちり計測してみました。

日産キックス600km試乗インプレ:80km/h以上の速度域では燃費が劇...

BMW320d ディーゼルの真骨頂! 1000km一気に走破 東京〜山形往復...

日産ノート | カッコイイだけじゃない! 燃費も走りも格段に洗練...

渋滞もなんのその! スイスポの本気度はサンデードライブでこそ光...

PHEVとディーゼルで燃費はどう違う? プジョー3008HYBRID4とリフ...

スズキ・ジムニーとジムニーシエラでダート走行の燃費を計ってみた...

会員必読記事|MotorFan Tech 厳選コンテンツ

フェアレディZ432の真実 名車再考 日産フェアレディZ432 Chapter2...

マツダ ロータリーエンジン 13B-RENESISに至る技術課題と改善手法...

マツダSKYACTIV-X:常識破りのブレークスルー。ガソリンエンジン...

ターボエンジンに過給ラグが生じるわけ——普段は自然吸気状態

林義正先生、「トルクと馬力」って何が違うんですか、教えてくだ...

マツダ×トヨタのSKYACTIV-HYBRIDとはどのようなパワートレインだ...

3分でわかる! クルマとバイクのテクノロジー超簡単解説

3分でわかる! スーパーカブのエンジンが壊れない理由……のひとつ...

3分でわかる! マツダのSKYACTIV-X(スカイアクティブ-X)ってな...

スーパーカブとクロスカブの運転が楽しいのは自動遠心クラッチ付...

ホンダCB1100の並列4気筒にはなぜV8のようなドロドロ感があるのか...

ホンダ・シビック タイプRの謎、4気筒なのになぜマフラーが3本?